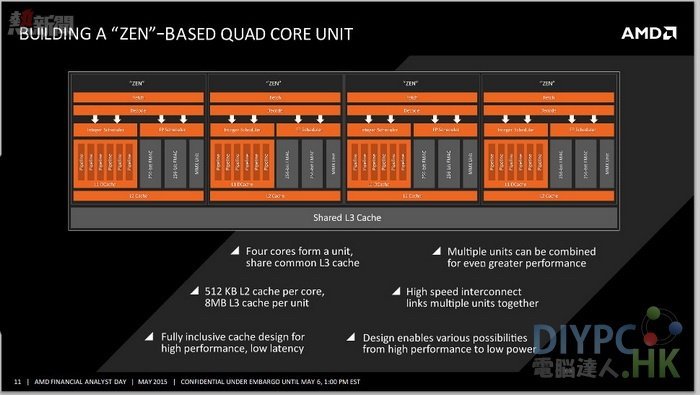

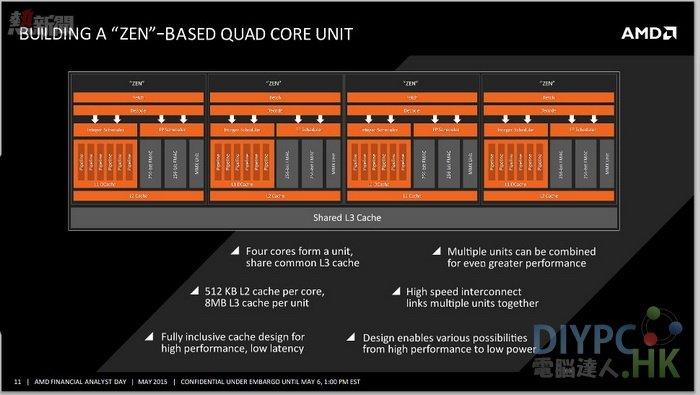

昨天有人曝光了AMD新一代X86架構Zen的核心圖,證實了AMD將放棄始於「推土機」架構的模組化多核設計,不過昨天的爆料只是核心的部份,今天有了更多細節——AMD的Zen架構中每個核心配搭512KB L2快取,而4個核心將組成一個單元,共享8MB L3快取,其中快取設計相比前幾代處理器有了重大變化,這種快取設計跟Intel的處理器設計類似。

有人曝光了AMD Zen架構的四核單元設計,跟昨天曝光的那個PPT應該同屬一份,這次重點披露的是AMD Zen架構多核心。從圖上看,AMD把四核Zen架構核心稱為一個單元,每個核心有自己的512KB L2快取,4個核心共享8MB L3快取。單從容量上來看,8MB L3快取的配置跟目前的模組化設計是相同的,512KB L2快取則只有「推土機」模組的一半容量,但實際上內部大有玄機。

AMD自從K6架構開始使用專有快取(exclusive cache)設計,快取之間的數據不通用,這種設計主要是為了提高快取利用效率,在「推土機」架構之前這都沒什麼問題。但是,影響模組多核性能的一個因素就是AMD的快取設計,快取關聯性太低,分支預測效率不高,命中率不高。

所以Zen架構中AMD的快取容量看起來小了,但快取改為inclusive cache,也就是說L1快取中的數據可以跟L2快取中的數據共享,這跟Intel的處理器快取設計是一樣的。

從圖片上來看,AMD一直在強調Zen架構的多核單元可以更高效地並聯,4個核心為一組單元,之前曝光過的16核Zen架構APU、32核Zen架構都可以此為基礎組合而成。

AMD Zen架構再次曝光,快取設計已經可同Intel相提並論

https://www.facebook.com/diypc.hk